我院信息科学与技术学部先进传感器件与集成系统重点实验室最近在深度学习处理器架构方面又取得新的进展。实验室微电子专业工学硕士研究生高曰超同学(导师为张盛副教授)发表的《面向深度卷积神经网络硬件加速优化的卷积核相对索引压缩编码格式》(Relative Indexed Compressed Sparse Filter Encoding Format for Hardware-Oriented Acceleration of Deep Convolutional Neural Networks)论文,在刚刚于中国台北召开的第八届下一代电子国际会议(The 8th International Symposium on Next-Generation Electronics,ISNE2018)上获得最佳论文奖。

该实验室基于当前学术和产业界主流的二维单指令多数据(2D-SIMD)处理器架构并进行了创新的改进,创新地提出了面向卷积核堆积数据流SFS和压缩编码格式CSF的3D-SIMD深度神经网络硬件加速处理器架构。与传统的2D-SIMD处理器结构相比,在使用AlexNet上的深度压缩后的数据时,处理单元(PE)阵列的利用率从26.5%提高到96.5%。在FPGA硬件验证实现时,该实验室的3D-SIMD处理器架构在大多数层上,每个PE的计算效率至少提高了2倍,特别是在AlexNet带有384个卷积核的层CONV4上实现了单个PE的计算效率8倍的提升,在经典网络VGG16带有512个卷积核的层CONV5-3上实现了11倍的提升。

实验室基于上述成果的论文《深度卷积神经网络硬件加速卷积核堆积数据流设计》(Stacked Filters Stationary Flow For Hardware-Oriented Acceleration Of Deep Convolutional Neural Networks,微纳电子系2015级硕士生高曰超为第一作者,导师张盛副教授为通讯作者)同时也在今年5月也入选了素有深度学习顶会“无冕之王”之称的国际深度学习表征会议(The 6th International Conference on Learning Representations, ICLR2018),高曰超同学赴加拿大参会并进行了现场成果展示,获得了深度学习硬件加速领域同业人员的高度关注。

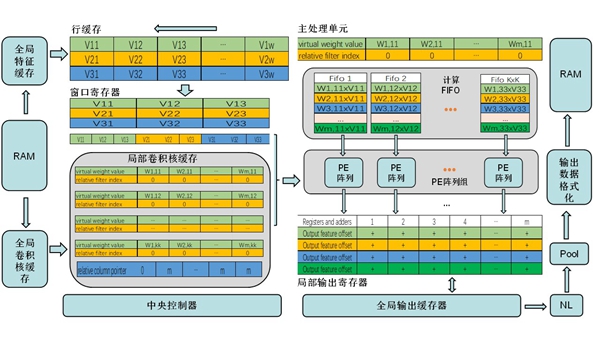

该3D-SIMD处理器架构中与输入特征相关的模块包括全局特征缓存、特征行缓存和特征窗口寄存器;卷积核相关的模块包括全局卷积核缓存和局部卷积核缓存;输出特征相关的模块包括全局输出缓存器和局部输出寄存器组。主处理单元包括计算队列组、PE阵列组和局部输出寄存器组。

SFS数据计算流程和CSF编码格式是3D-SIMD处理器架构的两个关键技术。在此架构中,单个输入特征通道数据加载到行缓冲区和窗口寄存器。当来自相同通道的m个卷积核数据被加载到本地缓冲器后,窗口中的每个元素将与相同位置的m个卷积核的一列数据相乘。按照设计,运行时可以直接处理和顺序加载由课题组独创的CSF格式编码数据,权重参数中的零值元素被直接跳过。这两种方法可以大大简化稀疏数据处理,节省旁路零值元素时钟以及数据查找时间。与以前的工作相比,本工作不需要复杂的稀疏数据处理逻辑。

此外,我院微电子方向在人工智能、大数据、物联网的芯片和硬件领域也取得了一系列的成果,包括驾驶行为识别研究成果发表于SENSORS顶级学术期刊、嵌入式云存储及eNDOS物联网操作系统实现千万元技术成果转化。尤其是在机器视觉领域,与产业公司合作开发的高动态CMOS图像传感器芯片实现了超过5000万颗,近5亿元市场销售,课题组任冠京同学毕业论文完成的流水线结构低功耗模数转换芯片IP、张浩同学毕业论文完成的图像信息处理算法的VLSI芯片IP,均在公司十余款图像传感器芯片产品中得到广泛应用,芯片成品应用于海康威视、大疆科技、大华股份等主流产业龙头企业,这为3D-SIMD架构卷积神经网络处理器芯片应用提供了坚实的产业化基础。

结合超高吞吐率和自定义指令集编程等特性,3D-SIMD处理器芯片架构可以应用于诸如高速工业相机等深度学习应用场景,作为通用可编程器件解决方案进行推广应用。

图为ICLR 2018上讲解3D-SIMD处理器架构

图为我院课题组提出的3D-SIMD深度学习处理器架构